Page 88 - Modul Elektronik Mata Kuliah Elektronika Daya (Tri Retno Puspitasari)

P. 88

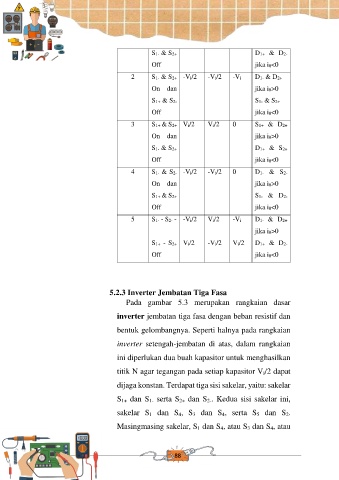

S1- & S2+ D1+ & D2-

Off jika i0<0

2 S1- & S2+ -Vi/2 -Vi/2 -Vi D1- & D2+

On dan jika i0>0

S1+ & S2- S1- & S2+

Off jika i0<0

3 S1+ & S2+ Vi/2 Vi/2 0 S1+ & D2+

On dan jika i0>0

S1- & S2+ D1+ & S2+

Off jika i0<0

4 S1- & S2- -Vi/2 -Vi/2 0 D1- & S2-

On dan jika i0>0

S1+ & S2+ S1- & D2-

Off jika i0<0

5 S1- - S2- - -Vi/2 Vi/2 -Vi D1- & D2+

jika i0>0

S1+ - S2+ Vi/2 -Vi/2 Vi/2 D1+ & D2-

Off jika i0<0

5.2.3 Inverter Jembatan Tiga Fasa

Pada gambar 5.3 merupakan rangkaian dasar

inverter jembatan tiga fasa dengan beban resistif dan

bentuk gelombangnya. Seperti halnya pada rangkaian

inverter setengah-jembatan di atas, dalam rangkaian

ini diperlukan dua buah kapasitor untuk menghasilkan

titik N agar tegangan pada setiap kapasitor V i/2 dapat

dijaga konstan. Terdapat tiga sisi sakelar, yaitu: sakelar

S 1+ dan S 1- serta S 2+ dan S 2-. Kedua sisi sakelar ini,

sakelar S 1 dan S 4, S 3 dan S 4, serta S 5 dan S 2.

Masingmasing sakelar, S 1 dan S 4, atau S 3 dan S 4, atau

88